Prihodnost superračunalništva: TSMC razkriva novo generacijo pospeševalnikov

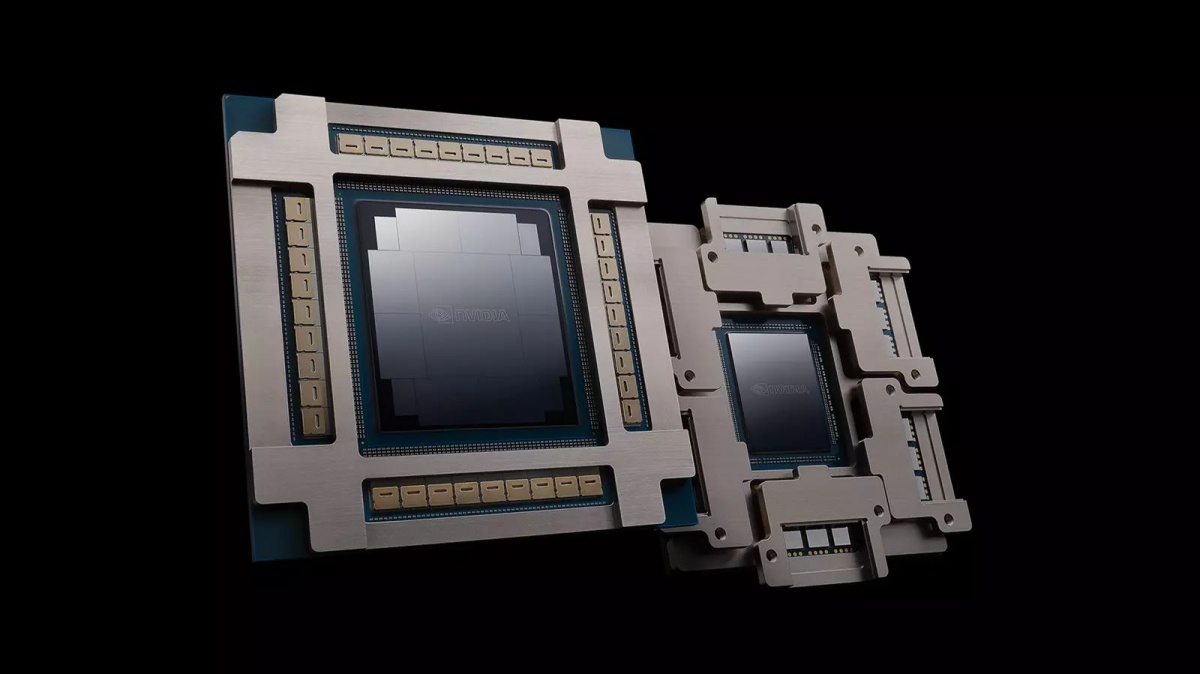

Na nedavni industrijski konferenci se je tajvanski polprevodniški gigant TSMC predstavil s futuristično vizijo pospeševalnikov, ki bodo temeljili na naprednih proizvodnih tehnologijah, zlasti na 2-nanometrski arhitekturi. Koncept, ki so ga prikazali, ni le tehnični prikaz možnosti, temveč kaže tudi strateško usmeritev podjetja – združevanje različnih čipov in tehnologij v enotno, zmogljivo in modularno rešitev, pripravljeno za zahtevna področja, kot so umetna inteligenca, visokozmogljivo računanje (HPC) in centri za obdelavo podatkov prihodnosti.

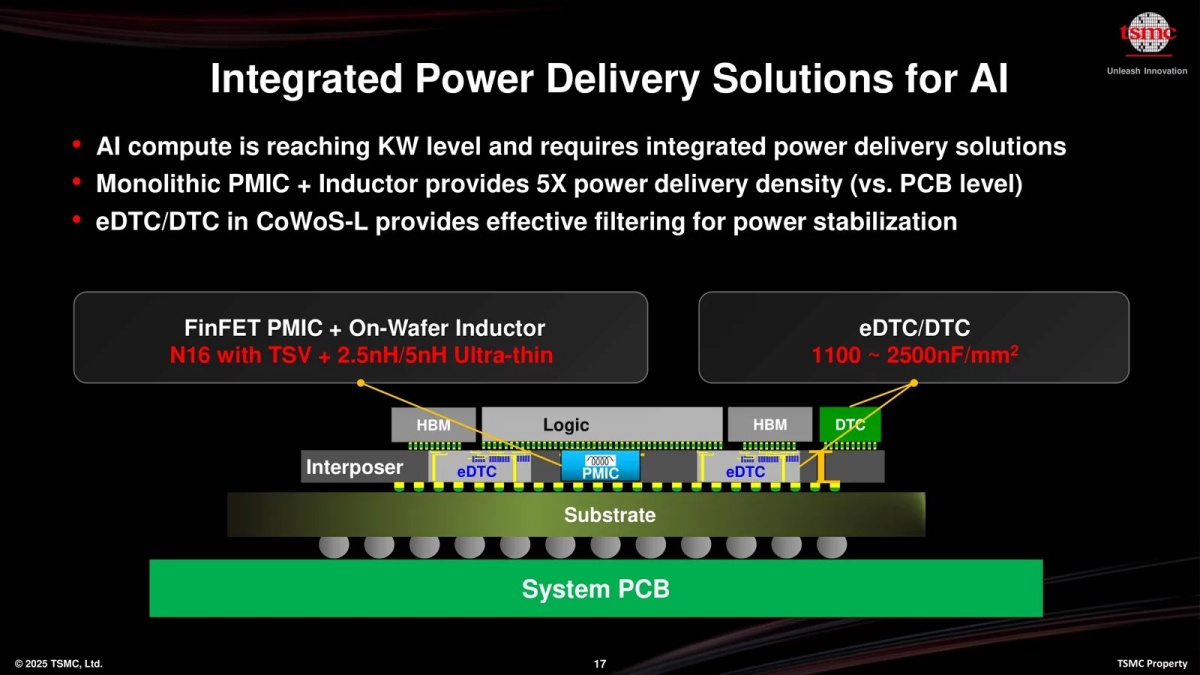

Jedro nove zasnove temelji na kombinaciji več čipletov, ki jih TSMC povezuje z lastnim vmesnikom z izjemno visoko prepustnostjo, imenovanim LSI (Local Si Interconnect). Pospeševalnik vključuje več procesorskih enot, ki temeljijo na 2-nanometrski tehnologiji N2, in jih obdaja pomnilniški podsistem HBM (High Bandwidth Memory), ki je vgrajen neposredno v paket. Vse skupaj je zasnovano v TSMC-jevi napredni 3D tehnologiji CoWoS (Chip-on-Wafer-on-Substrate), ki omogoča vertikalno zlaganje čipov in s tem bistveno večjo gostoto in zmogljivost ob nižji porabi energije.

Pomemben poudarek je tudi na prilagodljivosti in skalabilnosti. Prikazana arhitektura omogoča enostavno širitev s povezovanjem več takšnih enot v mrežo, kar odpira vrata sestavljanju superračunalniških gruč brez velikih izgub na zmogljivosti zaradi komunikacijskih ozkih grl. Poleg tega TSMC obljublja tesno integracijo s prihodnjimi generacijami pomnilnika HBM4 ter še učinkovitejše odvajanje toplote, kar bo ključno pri vzdrževanju zanesljivega delovanja pri ekstremnih obremenitvah.

TSMC s tem korakom jasno kaže, da želi igrati osrednjo vlogo v prihodnji generaciji zmogljivega računalništva, kjer čista moč ni več edini dejavnik uspeha – odločajo tudi energetska učinkovitost, modularnost in zmožnost hitre prilagoditve novim algoritmom in zahtevam. Nova arhitektura ni le tehnološki dosežek, temveč pomemben signal industriji, kako bo videti prihodnost pospeševanja računskih procesov – z več čipi, več nivoji povezljivosti in vedno tesnejšo integracijo.