Pet nanometrov je tu

Novi Applov iPhone 12 je prinesel novi procesor A14 Bionic. To je prvi komercialno dostopen izdelek, ki je zgrajen v 5-nanometrski litografiji, kmalu pa naj bi mu sledil tudi Qualcommov procesor. Manjše dimenzije prinašajo več tranzistorjev, večjo zmogljivost in manjšo porabo energije, a tudi številne izzive pri proizvodnji, ki jo trenutno obvladata zgolj dve podjetji na svetu. In nobeno v resnici ne proizvaja 5 nm velikih čipov.

Letos je sicer Apple nekoliko zamudil in ga ni predstavil na velikem jesenskem dogodku 15. septembra, ko so se razgovorili o novih pametnih urah in ipadih, temveč smo morali počakati še mesec dni. V novi generaciji iphonov, ki so jo pokazali 13. oktobra, tiktaka tudi nova generacija procesorjev. Apple je pri A14 Bionic posebej izpostavljal novi »nevronski« del procesorja (neural engine), ki je v Applovih procesorjih že od A11 in vsebuje vezja, ki so posebej prilagojena za izvajanje algoritmov, povezanih z umetno inteligenco, s strojnim učenjem in z nevronskimi mrežami. A14 ima kar 16 jedrc v tem delu procesorja (A13 jih je imel 8), ki lahko izvedejo 11 bilijonov operacij na sekundo. Zredil se je tudi celotni procesor, ki ima skoraj 40 odstotkov več tranzistorjev od predhodnika. Da jim je na 88 kvadratnih milimetrov, torej na manj kot kvadratni centimeter, uspelo stlačiti 11,8 milijarde tranzistorjev, pa so morali poseči po novi proizvodni tehnologiji. A14 je prvi komercialno dostopen izdelek, ki je zgrajen v 5-nanometrski tehnologiji. TSMC, ki ga proizvaja, litografijo imenuje N5.

Standardi

Čeprav si lahko vsak proizvajalec po svoje tolmači, kaj pomeni 7 ali 5 nm, vendarle obstajajo industrijska priporočila. ITRS (International Technology Roadmap for Semiconductors) je skupina dokumentov, ki so jih do leta 2017 pripravljali strokovnjaki industrije polprevodnikov. V teh priporočilih je bilo natančno opisano, katere metode (fotolitografija, jedkanje) in v kakšnih dimenzijah so potrebne, koliko so okvirne cene, katera opreme se potrebuje itd.

Od leta 2017 se uporablja IRDS (International Roadmap for Devices and Systems), ki vsebuje tudi napovedi, kako se bodo elektronske naprave in sistemi razvijali. IEEE označuje IRDS kot napovedi, ki so namenjene akademiji, industriji ter koordinaciji nabave in raziskav elektronike.

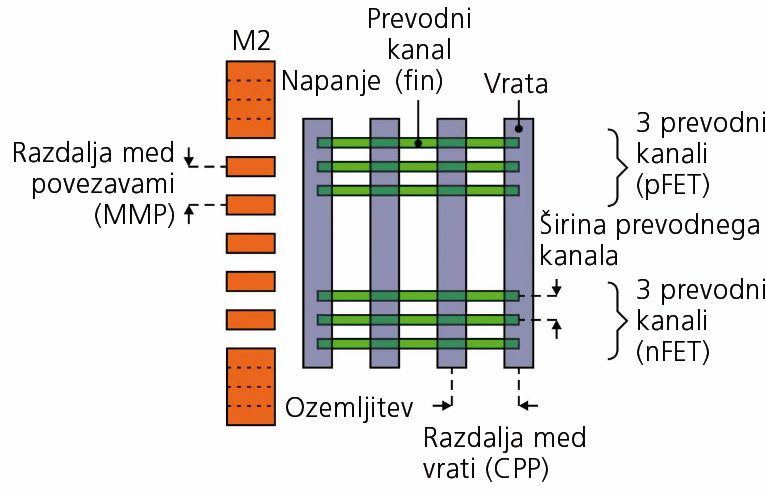

V načrtu iz leta 2017 je za 5 nm napovedano CPP 42 nm in MMP 24 nm. TSMC trenutno uporablja 48 nm in 30 nm, Samsung pa 57 nm in 36 nm. Samsungovi čipi so torej večji.

Še pred štirimi leti se je ta zdela znanstvena fantastika. Strokovnjaki so opozarjali, da se približujemo fizičnim mejam – ultimativna fizična meja je seveda velikost atoma –, saj krčenje tranzistorjev pomeni, da imajo njihovi sestavni deli čedalje manj atomov. To pa pomeni, da so kvantni efekti, ki se kažejo tudi kot presluhi, čedalje močnejši. Vsi pomembnejši proizvajalci so že tedaj trdili, da bodo slej ko prej obvladali 5 nm, le časovnice so bile sila nedorečene. Procesorji so bili tedaj še v 14 nm, mukoma pa je 10 nm postajal uporaben. Kot vmesna postaja je bila predvidena še 7-nanometrska litografija, zato so 5 nm previdno umeščali nekam po letu 2020. To še ni niti pri koncu, pa že imamo prvi komercialni izdelek v tej velikosti.

Ekstremni UV

Pomembno vlogo pri uveljavitvi te litografije je odigralo v javnosti manj znano nizozemsko podjetje ASML, ki je glavni dobavitelj sistemov za fotolitografijo v polprevodniški industriji. ASML je najprej razvil tako imenovano potopitveno litografijo. Z uporabo laserja iz argonovega flourida, ki proizvaja svetlobo valovne dolžine 193 nm, in vodo kot medijem (zaradi drugačnega lomnega količnika) je šlo leta 2011 do 32 nm. Takrat je ena taka naprava stala skoraj 30 milijonov evrov.

Ko niti 32 nm ni bilo več dovolj, je bila edina rešitev uporaba laserja s še krajšo valovno dolžino. Rezultat je ekstremna ultravijolična litografija (EUV), ki uporablja valovno dolžino 13,5 nm. Uporabljajo raztaljeni kositer, na katerega posvetijo z močnim industrijskim laserjem. To izpari kositer in ustvari plazmo, ki oddaja svetlobo UV ustreznih valovnih dolžin.

Prve naprave, ki so podpirale EUV, je ASML začel prodajati leta 2011. Dandanašnji posamezna stane 120 milijonov evrov, kar je veliko celo v svetu drage opreme za proizvodnjo čipov. A ASML je za zdaj edini proizvajalec teh kompleksnih naprav.

Fotolitografija pomeni, da čipe izdelujejo z jedkanjem s svetlobo. Na silicijeve rezine nanesejo na svetlobo občutljiv premaz, potem pa nanje posvetijo skozi masko, ki odseva (povečano) zgradbo čipa na določeni globini. Z lečami nato svetlobni vzorec pomanjšajo in usmerijo na površino čipa. Kjer pade svetloba na premaz, ta reagira, zato pri spiranju na čipu ostane enak vzorec kot na maski. Postopek se večkrat ponovi, saj so čipi zgrajeni iz mnogo plasti. Valovna dolžina ni stroga omejitev, pod katero se ne bi dalo iti, predstavlja pa omejitev velikostnega razreda. S 100-nanometrsko svetlobo pač ni mogoče jedkati čipov s subnanometrsko natančnostjo (več v Monitorju 10/19, Kako nastane čip).

V resnici pa je mogoče oblikovati čipe z nekoliko manjšimi karakterističnimi razdaljami od valovne dolžine svetlobe. Do 28 nm je šlo z eno masko. Da pa bilo mogoče uporabiti svetlobo z valovno dolžino 193 nm v 10-nanometrski tehnologiji (to ne pomeni, da so tranzistorji široki 10 nm!), se uporablja metoda večkratnega maskiranja (multipatterning). V tem primeru se za pripravo ene plasti uporabi več mask, ki se nekoliko zamaknejo, osvetlitev in jedkanja. Ker pa za 5 nm to vendarle ni bilo več zadosti, je bilo treba uporabiti EUV s 13,5 nm. Brez EUV bi potrebovali 35 mask, z njim pa jih po predvidevanjih TSMC zgolj 11–13.

Le dva na svetu

Ni dovolj kupiti naprave ASML za EUV, temveč jo je treba znati tudi uporabljati in ustrezno prilagoditi celoten proizvodni postopek. Trenutno sta taka le dva proizvajala čipov: tajvanski TSMC in južnokorejski Samsung. Intel naj bi začel tehnologijo uporabljati prihodnje leto (a kot 7 nm!). Še bolj zanimivo od tega, kdo tehnologijo uporablja, je, kdo je ne. Največji kitajski proizvajalec čipov SMIC (Semiconductor Manufacturing International Corporation) je želel stroje ASML kupiti, a je ameriška administracija to blokirala. Sama tega ni mogla storiti, saj v njih ameriške komponente ne dosegajo 25 odstotkov vrednosti, kar bi ZDA omogočalo blokado izvoza, zato so lobirali. Odkar je nizozemska vlada leta 2018 ASML podelila licenco za izvoz na Kitajsko, so ZDA začele intenzivno lobirati in leto pozneje dosegle, da nizozemska vlada licence, ki je potekla 30. junija 2019, ni podaljšala. SMIC bo tako prisiljen EUV razviti in izpopolniti sam. Trenutno so pri 14 nm, torej vsaj tri generacije v zaostanku. Tega ne bo mogoče hitro nadoknaditi, ugotavljajo analitiki pri Gartnerju.

Kod hodi Intel

Zdi se, da Intel zaostaja. Šele za prihodnje leto napovedujejo 7 nm, medtem ko se tehnologija 5 nm odmika v leto 2023. Drži tudi, da je imel z 10 nm nemalo težav in da to »ni najboljša tehnologija, kar smo jih kdaj imeli«, kot je dejal finančni direktor George Davis. Leta 2025 napovedujejo 3 nm, leta 2027 2 nm in do konca desetletja 1,4 nm. Zakaj je Intel tako počasen?

V resnici ni. Intel ima povsem primerljive težave kakor drugi proizvajalci. Morda je na nekaterih področjih nekaj mesecev ali največ kakšno leto v zaostanku, a Intel izdeluje drugačne procesorje kakor TSMC ali Samsung. Predvsem pa ima drugačen marketing. Intelovih 7 nm je primerljivih s 5 nm TSMC ali Samsunga. Enako velja za Intelovih 10 nm in konkurenčnih 7 nm.

Pri 10 nm je imel Intel CPP 54 nm. Enak CPP sta imela TSMC in Samsung pri 7 nm. MMP pa je imel Intel celo 36 nm, konkurenca pa (pri 7 nm) 46 in 40 nm.

Applove procesorje A14 Bionic, kot že mnogo generacij pred tem, proizvaja TSMC. Samsung pa po neuradnih podatkih za december pripravlja nov procesor družine Qualcomm, ki bo tudi izdelan v 5 nm. Telefon s procesorjem v tej tehnologiji je napovedal Huawei, za katerega bo čip Kirin 9000 za Mate 40 prav tako izdelal TSMC. Ta bo imel celo 15,3 milijarde tranzistorjev, kar je še 30 odstotkov več od A14. Razlog je nekoliko večji čip, ki ima vgrajen modem za 5G, medtem ko iphone uporablja ločen čip. Druga razlika je zmogljivejši grafični del (Mali-G78MP24) Huaweijevega čipa.

Med telefonoma iPhone 12 in Mate 40 pa obstaja pomembna razlika. Kot vse kaže, bo Mate 40 bolj nišni izdelek, saj TSMC zaradi ameriških sankcij – če se pod novo ameriško administracijo trgovinska vojna ne bo spremenila – od 15. septembra ne sme več proizvajati čipov za Huawei. Po ocenah ima Huawei 3–5 milijonov čipov in prav toliko bo tudi telefonov. Naročili so jih bili 15 milijonov. V 5-nanometrski tehnologiji obdelana silicijeva rezina pri TSMC stane 17.000 dolarjev, medtem ko je za 7-nanometrsko ta dobrih 9.000 dolarjev.

Zakaj manjše

Ob vsem navdušenju nad miniaturizacijo seveda ne smemo pozabiti povedati, zakaj je to sploh pomembno. Manjši tranzistorji pomenijo, da jih lahko na enako površino stlačimo več. Ker pametnih telefonov (ali tudi osebnih računalnikov) ne moremo bistveno povečati, je to edini način, da jim povečamo računske zmogljivosti in omogočimo izvajanje zahtevnejših operacij. Danes napredek ne gre več v višje takte, temveč v povečevanje števila jeder (med katerimi najdemo tudi namenoma počasna, ker so varčnejša) in dodajanje specializiranih enot, denimo za umetno inteligenco, prepoznavanje govora, obdelavo slik, šifriranje ipd.

Druga zelo pomembna posledica pa je zmanjševanje porabe električne energije. Manjši tranzistorji potrebujejo nižje napetosti in nasploh porabijo manj energije. Ker se na koncu vsa pretvori v toploto, se taki čipi manj grejejo. S starimi, potratnimi čipi sploh ne bi bilo mogoče izvesti toliko operacij kot z novimi, ker bi se preprosto pregreli. Pri mobilnih napravah pa manjšo porabo energije namesto v povečevanje zmogljivosti raje pretopijo v daljšo avtonomijo. Pričakovati je, da bomo v prihodnosti videli čedalje več naprav s 5-nanometrskimi čipi.

Kaj pomeni 5 nm

Prvih 35 let polprevodniške industrije, približno do sredine 90. let, je oznaka litografije dejansko pomenila, kako široka so vrata (gate) na tranzistorju (MOSFET). Na prelomu tisočletja se je ta pomen počasi izgubil. Intel je leta 1997 v 0,25-mikronskem procesu uporabljal širino vrat 200 nm (0,20 μm), v 0,18-mikronskem pa 130 nm.

Pred približno 14 leti je bila širina vrat v 45-nanometrski tehnologiji 25 nm, kar je spodnja fizikalna smiselna meja. Odtlej je širina vrat bolj ali manj konstanta, krčijo pa se nekateri drugi parametri. Od prihoda FinFET in tridimenzionalnih čipov je poimenovanje velikosti litografije v nanometrih izgubilo jasno povezavo z resničnostjo. Nedvomno drži, da je vsaka naslednja iteracija z nižjo številko prinesla večjo gostoto tranzistorjev na površini, ne gre pa številčne vrednosti jemati za suho zlato. To pa pomeni tudi, da bosta 5-nanometrski tehnologiji iz TSMC in Samsunga lahko drugačni in verjetno tudi bosta. V praksi so 10 nm iz Intela ter 7 nm iz TSMC in Samsunga zelo podobni. To je marketing.

Pri TSMC se 5-nanometrski postopek proizvodnje imenuje N5 in v primerjavi z N7 nudi 15 odstotkov več hitrosti in 30 odstotkov manjšo porabo energije. Pripravljajo že njegovo nadgradnjo N5P, ki bo od N7 20 odstotkov hitrejši in 40 odstotkov varčnejši. Gostota elementov je 171,3 MTr/mm2 (za N7 pa 115,8 MTr/mm2). N7 so začeli uporabljati leta 2018, torej TSMC potrebuje približno dve leti za pomanjšavo litografije.

Ključna parametra za opis dejanske velikosti litografije se imenujeta CPP (contacted poly pitch, tudi transistor gate pitch) in MMP (minimum metal pitch). Pitch predstavlja širino elementa in razdaljo do sosednjega elementa. Pri CPP so to vrata tranzistorja, pri MMP pa prevodne povezave med tranzistorji (interconnect). CPP predstavlja širino. Pri N5 je CPP 48 nm, MMP pa 30 nm. Njun produkt predstavlja velikost celice.