Inženiring za naslednje desetletje Moora

Uporabniki smo navajeni, da vsako leto ali dve prispejo nove in hitrejše generacije čipov vseh vrst. Takšen tempo pa zahteva vse večji trud strokovnjakov in tehnologije, ki so vse bolj zapletene.

Planarni MOSFET tranzistor je dobro služil pol stoletja, FinFET dobrih deset let. Industrija se sprašuje, kakšno življenjsko dobo bo imel naslednik, GAAFET, ki trenutno vstopa v uporabo.

Poigravanje z vprašanjem, ali Moorov zakon še velja, je običajen »šport« na vsaki resnejši računalniški konferenci. Torej ali procesorji tudi dandanes še dosledno napredujejo v zmogljivosti, kot so doslej? Okviren odgovor je še vedno pritrdilen, četudi smo natančno definicijo tega »zakona« – ki je v bistvu zgolj opažanje – vmes že nekajkrat priredili. In če sodimo po načrtih, ki so jih v letošnjem letu objavili pri tajvanskem proizvajalcu TSMC in pa belgijskem vodilnem razvojnem centru Imec (o katerem smo pisali v prejšnji številki), se v bližnji prihodnosti to ne bo spremenilo. Vendarle pa te časovnice poleg optimizma vnovič razkrivajo tudi boleče dejstvo, ki nam je že dolgo znano: z manjšanjem elementov v čipih neobhodno trčimo ob meje, ki jih postavljajo fizikalni zakoni, zato morajo biti prijemi, ki jih uporabljajo snovalci elektronskih vezij na čelu napredka, vse bolj domiselni in dih jemajoči.

Varljivi nazivi

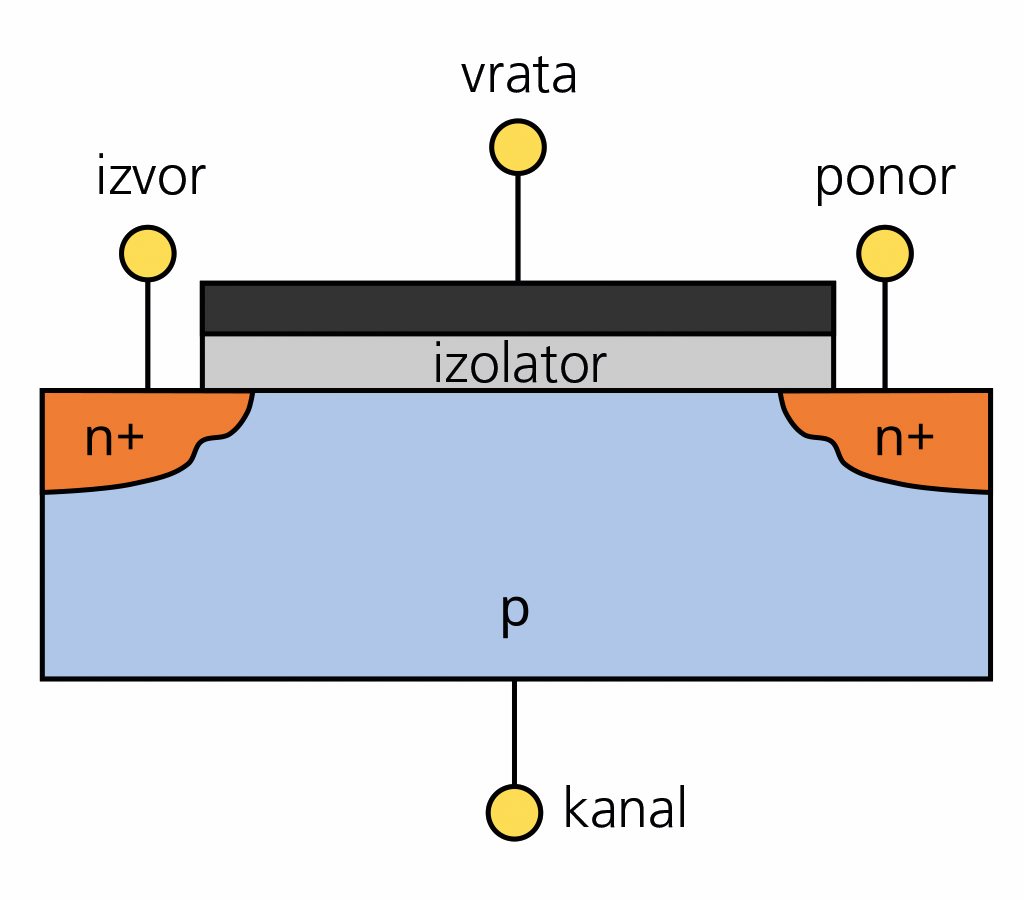

Do pred nekaj več kot desetimi leti smo zmogljivost čipov v splošnem povečevali s premočrtnim pomanjševanjem gradnikov, ki jih sestavljajo. To se pravi, izdelovali smo tranzistorje z vse krajšo razdaljo med izvorom in ponorom, vse ožje žičke, ki jih napajajo, in tako naprej. To se je najprej prevedlo v golo množenje računskih zmogljivosti, ker je elementov na določeni površini lahko več. Hkrati so krajše razdalje omogočale tudi doseganje višjih frekvenc, s katerimi čipi izvajajo ukaze, zaradi česar so imeli procesorji vse več megahercev. Generacije proizvodnih procesov so bile zato takrat dokaj enolično označene z mero najmanjšega diskretnega elementa, ki smo ga s takšno tehnologijo lahko napravili. Na prelomu tisočletja je kraljeval 130-nanometrski proces, kar v grobem pomeni, da je bil kanal v tranzistorju, po katerem nosilci naboja potujejo med izvorom in ponorom, dolg okoli 130 nanometrov, to je milijonink milimetra.

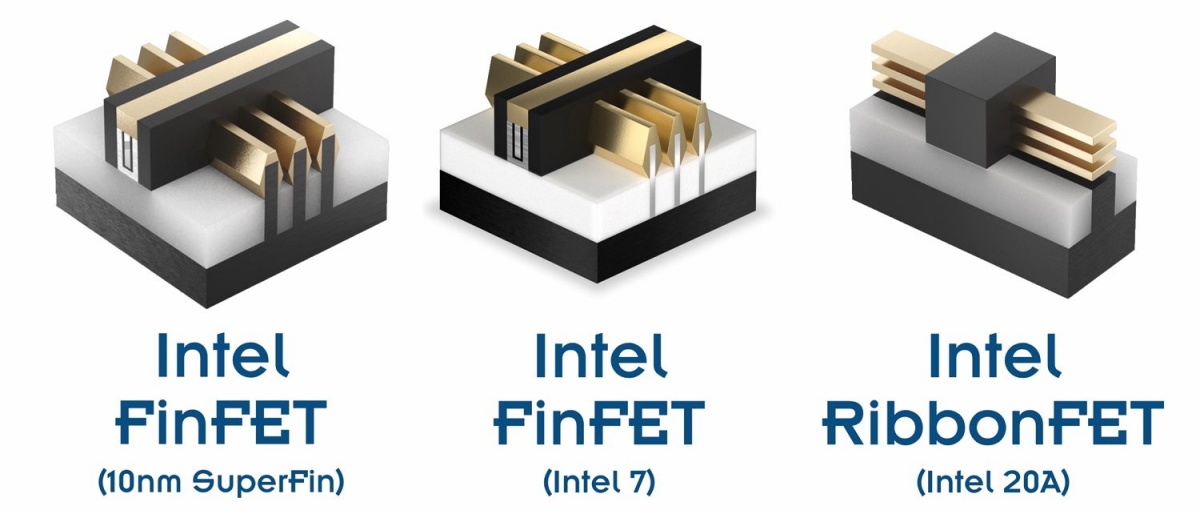

Po letu 2010 se je situacija zapletla. Mere so se skrčile pod 30 nanometrov, kjer so inženirjem začeli močno mešati štrene kvantni pojavi. Natančneje, parazitski tokovi so tekli tudi, ko so bili tranzistorji ugasnjeni. Strokovnjaki so se zato lotili prenove starega dobrega planarnega tranzistorja, ki je bil dotlej glavni delovni konj. Pri takšnem tranzistorju ima kanal obliko kvadra iz silicija, na katerega je poveznjen drug kvader silicija – to so vrata, ki s svojo napetostjo preklapljajo tok skozi kanal. Da bi ojačali nadzor vrat nad kanalom, so se domislili zasnove, pri kateri ima kanal obliko plavuti, ki štrli iz ravnine, vrata pa jo ovijajo s treh strani. Zaradi plavutastega (fin) videza je takšen tip tranzistorja dobil ime FinFET, za fin field-effect transistor. Prvi so ga leta 2012 uvedli pri Intelu pod imenom Tri-Gate za procesorje arhitekture Ivy Bridge na 22-nanometrskem procesu. Leto pozneje sta sledila še Samsung in TSMC.

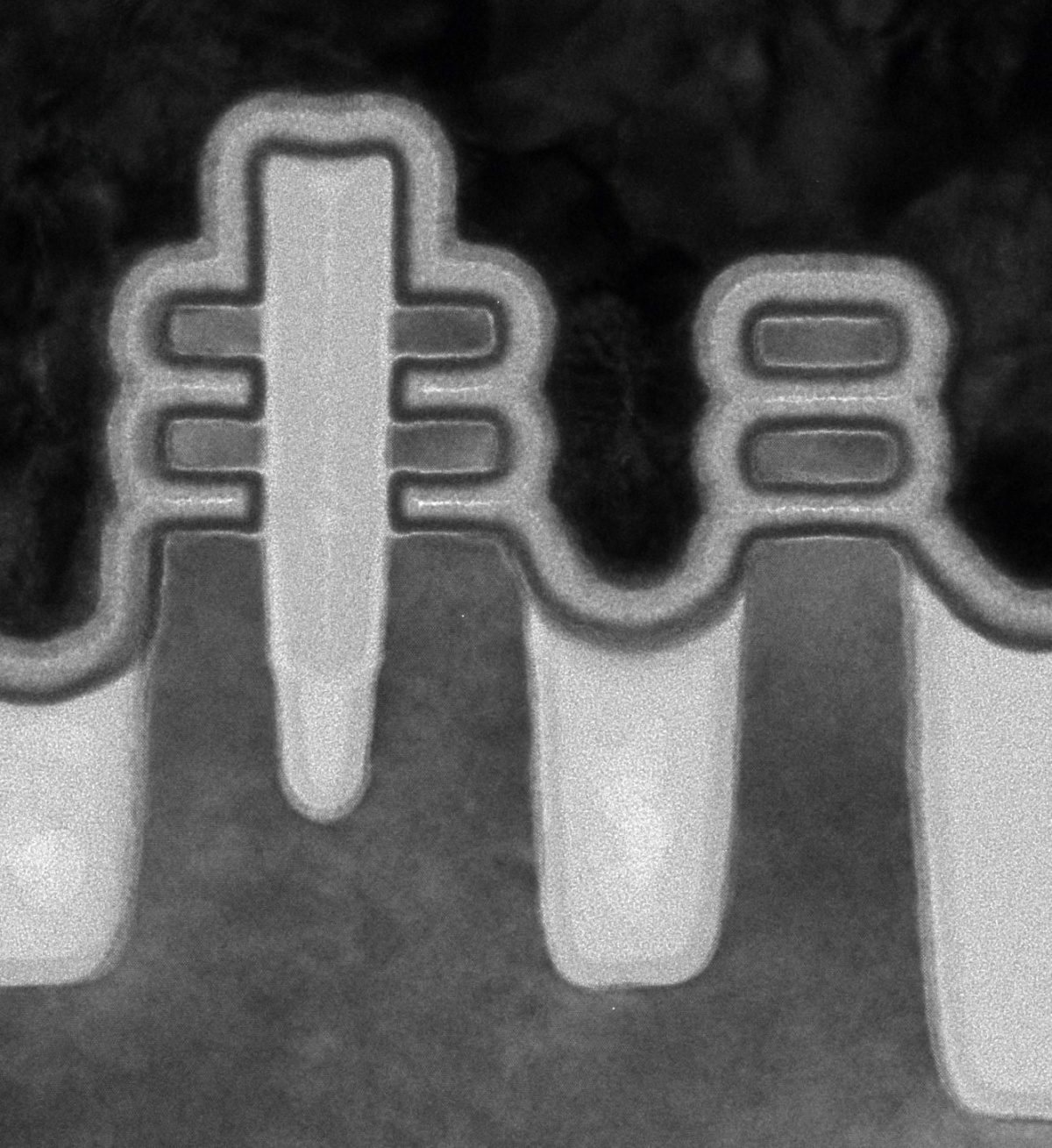

Dva najmodernejša tranzistorja pod mikroskopom, od strani. Na desni GAAFET z dvema lističema, na levi pa forksheet, ki bo očitno vmesni korak do tranzistorjev CFET.

Pomemben »hakeljc« je sledil v dejstvu, da je pojav tranzistorjev FinFET porušil enolično povezavo med nazivi proizvodnih procesov in dimenzijami gradnikov v čipih. Takšni tranzistorji so namreč povečali zmogljivosti vezij brez znatnejših preskokov v velikosti elementov in proizvajalci so bili pred kočljivo marketinško dilemo: ali uvesti povsem novo shemo poimenovanj generacij proizvodnje ali nekako nadaljevati obstoječi način. Odločili so se za rešitev, ki še danes velja za kontroverzno: procese poimenujejo z ekvivalenti planarnega modela. To se pravi: kako velik bi bil ekstrapolirani planarni tranzistor, da bi imel zmogljivost, ki jo imamo v rokah. To pomeni, da so bila pri »7-nanometrskem procesu« tranzistorska vrata v resnici dolga 20 nanometrov. Bolje kot na papirnate oznake se je zato zanašati na stvarne preizkuse.

»Šnelkurs« modernega tranzistorja

Osnova elektronskih logičnih vezij so stikala, ki glede na vhodne signale prepuščajo ali ustavljajo tokove, s katerimi izvajamo logične ukaze. Fizična implementacija takšnih stikal v današnjih čipih je tranzistor vrste MOSFET, kar je kratica za metal-oxide semiconductor field-effect transistor. Sestavljen je iz izvora nosilcev naboja in njihovega ponora, vmes pa je kanal, po katerem potujejo. O prepustnosti kanala – in torej pretikanju stikala – odločajo vrata, in sicer na način, da na kanal delujejo z električnim poljem, ko je nanje pritisnjena napetost. Od tod drugi del kratice FET. Prva polovica kratice, MOS, pa pove, da so vrata od kanala fizično ločena s plastjo izolatorja, silicijevega oksida.

Objem električnega polja

Trenutno spremljamo nov prelomen preskok, kajti proizvajalci bodo obliko tranzistorja spet spremenili, drugič v zgodovini. Po dobrih desetih letih je namreč tudi FinFET odslužil svoje, saj plavutasti kanal nosilcev naboja ne more več zadrževati tam, kjer bi si želeli. Sledi rešitev, ki se na prvi pogled sliši sila logična: v prihajajočih tranzistorjih bodo vrata kanal ovijala z vseh strani, okoli in okoli. Od tod tudi ime: gate-all-around field-effect transistor ali GAAFET. V Intelu morajo biti vnovič nekaj posebnega, zato novost imenujejo RibbonFET, medtem ko ji v Samsungu pravijo tudi MBCFET za multi-bridge channel FET. Ponekod, recimo pri Imecu, je zato mogoče opaziti še nekakšen krovni, oglaševalsko nevtralen naziv, to je nanosheet, ki ponazarja, da kanal tranzistorja sestavljajo tanki lističi, ki jih ovijajo vrata.

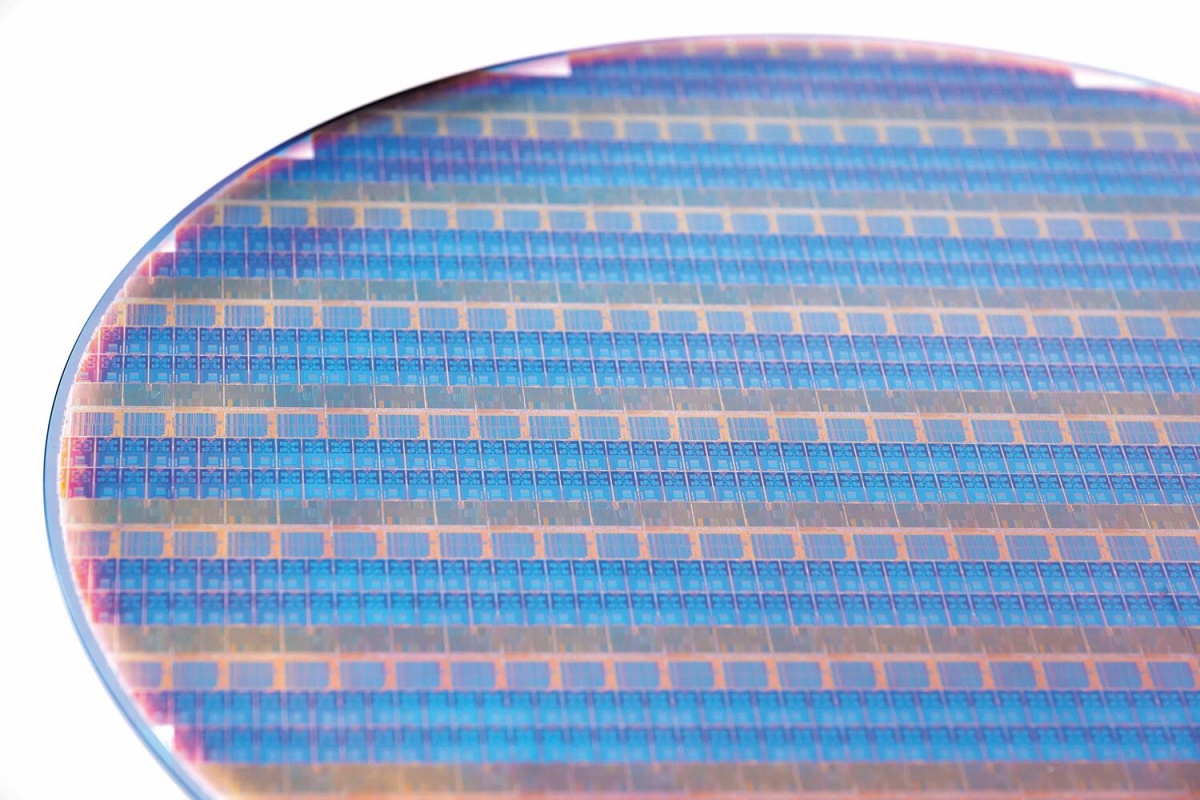

A kar je resda dokaj premočrtna izboljšava, je zahteven inženirski izziv, ker zahteva konkretno nadgradnjo proizvodnje. Za najboljši pretok nosilcev naboja kanal tranzistorjev GAAFET sestavlja več nadstropij lističev, ki jih ovija material vrat. Takšne strukture izdelajo na način, da na silicijevo rezino najprej izmenično nanašajo plasti materiala kanala in vrat, nakar jih z jedkanjem izdolbejo v končno obliko. To zahteva bistven preskok predvsem v zmogljivosti in natančnosti depozicije, torej nanosov plasti materiala. Pri procesu fotolitografije, s katerim proizvajamo integrirana vezja, tradicionalno z jedkanjem v silicijevo rezino izdolbemo jarke in vanje nanesemo preproste strukture, kot so bakrena vodila. Nanašanje več plasti natančno odmerjenih materialov pa je za razred zahtevnejše početje.

Ledino orjejo pri Samsungu, kjer so tranzistorje GAAFET že pred tremi leti eksperimentalno preizkušali v manjših čipih za rudarjenje kriptovalut, zdaj pa so na vrsti v njihovem 3-nanometrskem procesu. Prvi izdelek z njimi je bil julijski telefon Galaxy Z Flip 7 s sistemskim čipom Exynos 2500. V Intelu nameravajo tranzistorje GAAFET uvesti s procesom 18A (A za angstrom, to je desetina nanometra) konec tega leta. Še najbolj zadržani so pravzaprav v TSMC, zmagovalcih dobe FinFET. Tajvanci bodo namreč novo vrsto tranzistorjev previdno uvedli s procesom N2 na prehodu v prihodnje leto. Da tega niso storili že pri N3, ki je njihovo trenutno čelo napredka, se vse bolj kaže kot odlična odločitev, saj imajo po odzivih strank sodeč boljši izkoristek proizvodnje od konkurence. Izmet naj bi bil zgolj okoli 10-odstoten, medtem ko naj bi bil Samsungov kar blizu polovice! Google naj bi ravno zaradi tega proizvodnjo telefonskih procesorjev Tensor G5 (najdemo jih v najnovejšem telefonu Pixel 10) prenesel iz Samsunga v TSMC. Zadnje tedne pa se vse bolj šušlja, da ima resne težave z načinom 18A tudi Intel …

Hitro hujšanje

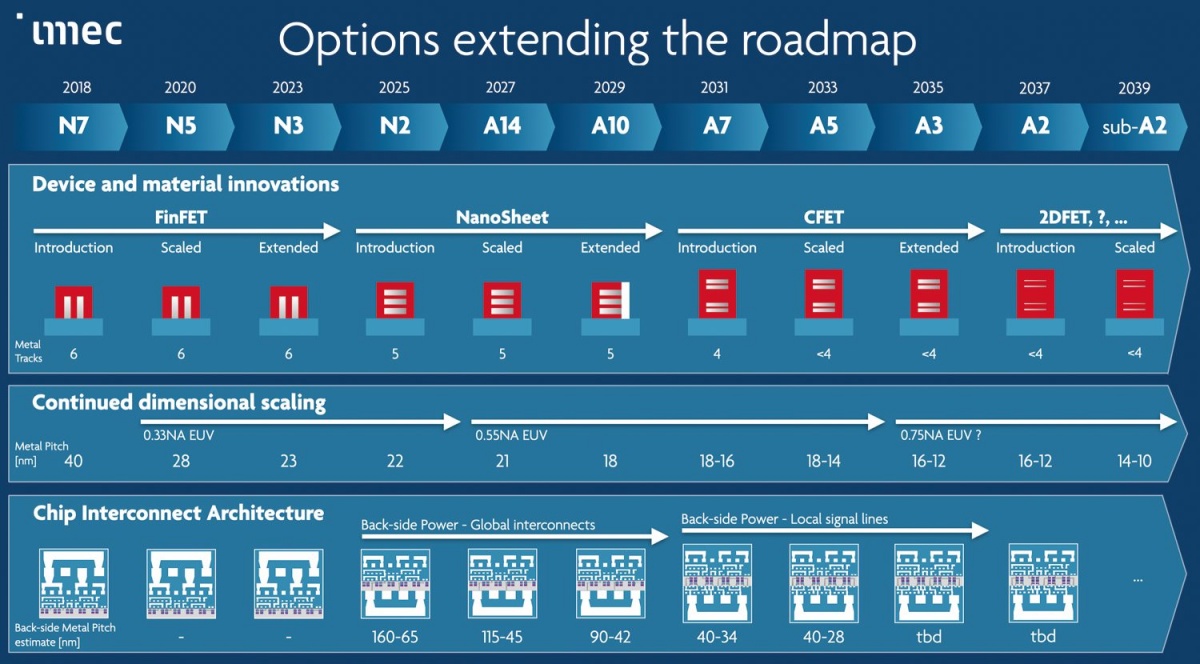

Imecova časovnica, ki so jo potegnili kar do leta 2039, nam pove tudi, kaj verjetno pride za stikali GAAFET. To so tranzistorji complementary FET ali CFET, in sicer po letu 2031. Njihova razlaga zahteva nekaj predznanja o osnovah računske logike v večjih integriranih vezjih, predvsem podrobnost, da tranzistorji običajno nastopajo v dvojicah, pri čemer je eden vrste NMOS, drugi pa PMOS. Razlika med njima je v nosilcih naboja: pri prvih so to elektroni, pri drugih pa vrzeli. To razliko inženirji dosežejo na način, da siliciju dodajo različne primesi drugih kemijskih elementov – pravimo, da ga dopirajo. Dvojica tranzistorjev NMOS in PMOS sestavlja sistem CMOS, za complementary metal-oxide semiconductor, kar je nekakšna osnovna enota, iz katere so sestavljena logična vezja v čipih.

Imecova časovnica, ki predvideva razvoj do leta 2039. V članku smo prišli do leta 2035; nato pridejo na vrsto pravi 2D materiali, se pravi takšni, debeli zgolj eno molekulo ali atom. O njih je še mnogo neznank.

Tranzistor CFET to dvojico tranzistorjev združi v enem samem, in sicer na način, da je polovica lističev, ki sestavljajo strukturo GAAFET, dopirana na en način, druga polovica pa na drugega. Vmesna stopnica do CFET bi lahko bil tako imenovani forksheet tranzistor, ki smo ga omenili v prispevku o Imecu: tu je sveženj lističev kanala preboden s plastjo izolatorja, pri čemer na eni strani ostanejo p-dopirani lističi, na drugi pa n-dopirani. Smisel zasnove CFET je očitna: z njo bi se velikost enote CMOS dobesedno prepolovila! To bi imelo precej korenite posledice tako za velikost kot zmogljivost čipov, zato bo prihod te tehnologije gotovo zanimivo spremljati. A do takrat morajo strokovnjaki streti še dosti tehničnih orehov. Že pri nizanju plasti ene vrste polprevodnika se srečujejo z velikimi izzivi. Nalaganje različno dopiranih plasti pa bo brez dvoma posebne vrste umetnost.

Predori skozi silicij

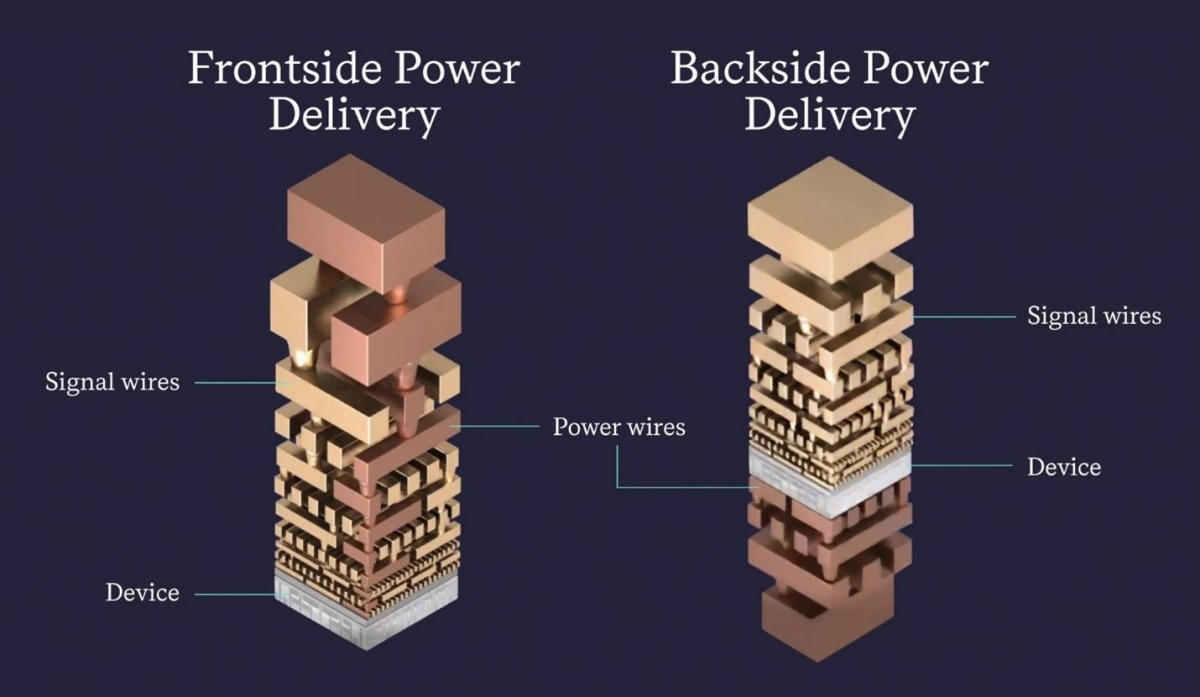

Pustimo zdaj pri miru Imecove poglede v daljno prihodnost in pokukajmo še izza meja tranzistorjev, kajti napredek pri velikih čipih prinašajo tudi druge vrste tehnologij. Tista, ki bo v bližnji prihodnosti najbolj v ospredju, nosi ime backside power delivery network ali BSPDN. Kot lahko sklepamo, se tiče dostavljanja elektrike elementom v integriranih vezjih. To se morda zdi postranska zadeva v primerjavi s samimi tranzistorji in podatkovnimi tokovi, toda v resnici sestavlja znaten del dizajna večjih čipov – ker zase zahteva tudi znaten del prostora v njih. Elektriko je pač treba speljati do slehernega elementa čipa; to se pravi: tisti kabel, ki ga priklopimo na matično ploščo, se mora v čipu razvejati na nešteto manjših, preden pride do posameznih tranzistorjev. To poteka skozi številna nadstropja vse ožjih bakrenih vodil – tam do dvajset ravni! Omrežje teh žičk ima zato podobo orjaške prepletene goščave, ki se vije nad ploskvijo z dejanskimi logičnimi elementi. To ima konkretne posledice. Prvič, zaradi upornosti bakrenih žičk se dosti moči na poti »navzdol« izgubi v obliki toplote. In drugič, ker je treba v istem prostoru speljati tudi podatkovna vodila, moramo paziti, kako pletemo vodila ene in druge vrste, da se med seboj ne motijo. To poveča zamik v podatkovnih tokovih, ker se morajo ti izogibati električnim in potovati naokoli.

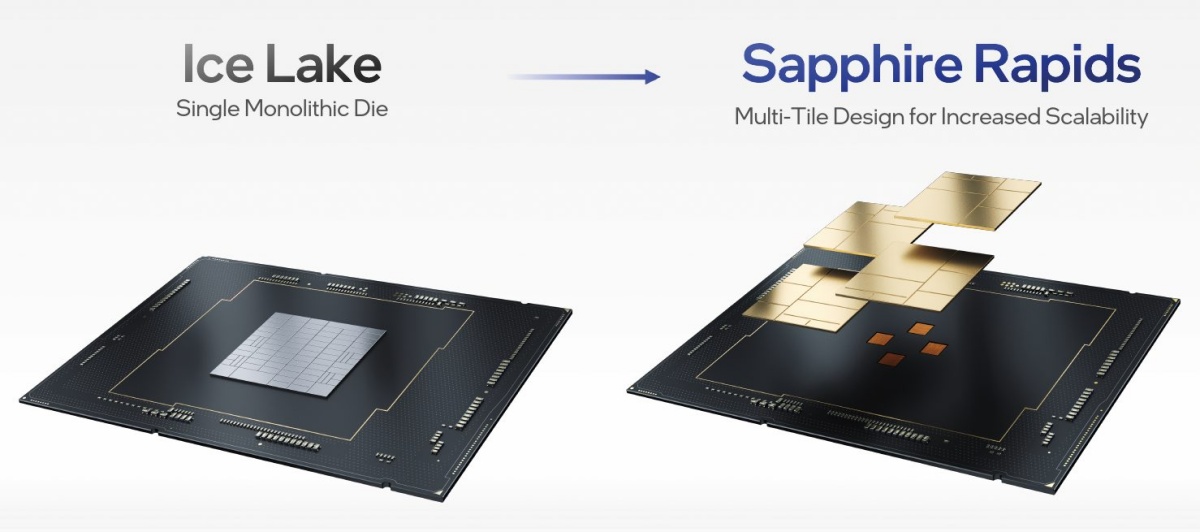

Industrija je morala še pred prehodom na 3D čipe obvladati spajanje večjih diskretnih gradnikov, kar je težje, kot se zdi na prvi pogled. Predstavljajte si, da je bunkica lego kocke, ki jo je treba postaviti na pravo mesto, široka deset nanometrov.

Namesto tega so v Imecu predlagali, naj se celotno napajalno vejevje premakne na nasproten, spodnji konec čipa. Tako si napajalna in podatkovna vodila ne bodo več v napoto ter bodo ena in druga lahko krajša, kar bo pripeljalo tako do manjše porabe kakor manjšega zamujanja podatkov. Študije z univerz kažejo, da naj bi bila električna poraba manjša za slabo desetino, še pomembnejši pa je podatek, da lahko tako na koncu goščave žičk – pri samih tranzistorjih – dosežemo sedemkrat višjo napetost. Najpogumnejši pri udejanjanju te zamisli so v Intelu, kjer nameravajo BSPDN uvesti v že omenjeni generaciji procesa 18A. To se pravi, da so v Santa Clari pri tem proizvodnem načinu izjemno ambiciozni, saj poleg nove vrste tranzistorjev prinaša še povsem nov način njihovega napajanja. Strokovna javnost se sprašuje, ali si niso nemara vnovič nakopali pretežkega bremena. Bistvene izbire Intel v resnici ni imel, saj mora loviti zaostanek za TSMC in takšna zasnova 18A je v mnogočem usmerjena v njegovo izničenje.

Za kakšen tehnični izziv gre, lahko preprosto ponazorimo z dejstvom, da je treba tu silicijevo rezino obdelovati z obeh strani, ne samo z ene. Pri tem se najprej izdolbe vodoravne kanalčke na obeh straneh in »položi« najbolj fina vodila iz volframa ali rutenija na zgornji strani, nakar je treba izdolbsti navpične kanalčke, ki jim pravimo TSVs (through-silicon vias), da se prebijejo skozi rezino. Te kanale »vrtajo« s curki plazme in so široki manj kot sto nanometrov, pri čemer morajo biti presneto natančni, da jih vrežejo na ravno pravih mestih, da na drugi strani ne pogledajo ven na napačnem koncu. Razumljivo je, da so v TSMC ubrali previdnejšo možnost in bodo najprej v generaciji procesov N2 uvedli zgolj tranzistorje GAAFET, ozadno napajanje pa šele generacijo za tem, to je pri A16 v letu 2027.

Grajenje v višino

Tretji poglavitni sklop tehnologij, ki danes narekuje trende v razvoju procesorjev, pa je siljenje v (pol)tretjo dimenzijo, torej nalaganje integriranih logičnih vezij v več plasti. Dejavnost je tesno povezana s pojmom »pakiranja« (packaging), s čimer označujemo povezovanje izdelane silicijeve plasti z logičnimi vezji (die) zunanjega sveta. Donedavna je to pomenilo preprosto polaganje dokončanega koščka integriranega vezja na debelejši substrat, ki mu je dajal fizično oporo in zaščito, hkrati pa ga je skozi priključke povezoval z vtičnico na matični plošči oziroma s podnožjem. Trenutno smo sredi navdušujoče revolucije pakiranja, ki vlogo substrata poglobi in strukturi čipa doda kup elementov. Integrirano vezje ni več sestavljeno iz ene plasti silicija, ki vsebuje eno plast s tranzistorji. Razbili smo ga na manjše ločene kosce čiplete (chiplets), ki sami zase sestavljajo, denimo, procesni sklop, vhodno-izhodni sklop in tako dalje. Povezuje jih vmesnik ali interposer, to je namenska plast silicija, na katero so postavljeni. Če vsebuje zgolj podatkovne in napajalne povezave, je to pasivni vmesnik. Če pa je zmožen tudi omejene obdelave podatkov – na primer pametnega razpošiljanja elektrike –, mu pravimo aktivni vmesnik.

V shemah komunikacijskih vodil je vidna zapletenost omrežij, ki tranzistorjem dostavljajo signale in napajanje. Nekoč smo za žičke uporabljali aluminij, konec devetdesetih ga je zamenjal baker.

Splošno razširjena današnja raba čiplete postavlja enega ob drugega na vmesnik. Za takšno strukturo se je udomačila oznaka 2.5D. Če pa gredo v več nadstropij tudi sama logična vezja, to imenujejo 3D. Primer sta pomnilnik HBM, ki ga postavljajo v mnoga nadstropja, ali medpomnilnik L3, ki je v procesorjih AMD Ryzen X3D poveznjen čez čiplete. Najmodernejše zasnove ti dve shemi združujejo in »3D-pomnilnik« HBM skozi interposer postavijo ob bok računskim čipletom, kar lahko vidimo v velikih čipih GPGPU za pospeševanje strojnega učenja. V AMD imajo trenutno komično namero, da bi prepričali industrijo, naj pristop poimenuje 3.5D. V končni fazi vse sili v takšno spajanje večjih gradnikov v treh razsežnostih, in sicer iz dveh razlogov. Čipleti kot gradniki so v osnovi varčevalni prijem, saj lahko v primeru napake zavržemo zgolj posamezen čiplet, ne celotnega čipa. In drugič, potovanje v vertikalo pomeni krajše povezave med različnimi sklopi čipa, s tem pa manjše zamike in večje hitrosti potovanja podatkov.

Verjetno nam ni treba poudarjati, da so tudi tehnične prepreke na poti do procesorjev v obliki nanonebotičnikov gromozanske. Ni še povsem jasno, kako bomo učinkovito odvajali toploto iz sredice takšnih čipov, ali pa, kako jih v fazi preverjanja natančno pregledovati v iskanju defektov. Potrebni bodo novi preboji v vrsti tehnologij, kot je spajanje silicijevih plasti med seboj, pa verjetno nove vrste substratov, kot so stekleni, s katerimi trenutno eksperimentirajo zlasti v Intelu. Toda neusmiljenost fizikalnih zakonov inženirje sili v vse mogoče smeri, če želijo Moora še naprej ohranjati pri življenju. In ravno zato področje polprevodniških vezij še nikoli ni bilo tako zanimivo.