Čipi v treh razsežnostih

Inženirji razmišljajo o tem, kako na čedalje manjši prostor stlačiti čedalje več tranzistorjev in drugih elektronskih elementov ter električnih povezav. Ko se miniaturizacija komponent počasi bliža fizikalnim omejitvam, so se domislili nove zvijače, ki jo arhitekti poznajo že tisočletja. Čipe bi lahko zlagali tudi v višino.

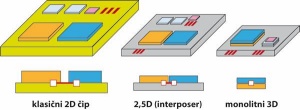

V 2D čipih so elementi in povezave med njimi v isti ravnini. V 2,5D so povezave umaknjene na svoj nivo. V monolitnih 3D čipih so tudi elementi v različnih ravninah in medseboj vertikalno povezani.

Prvi računalniki so za krmiljenje in ojačevanje signalov uporabljali elektronke. Te so bile okorne, velike, občutljive in nezanesljive, zato so bili takšni tudi prvi računalniki. Vse to se je spremenilo, ko so v Bellovih laboratorijih leta 1947 iznašli polprevodniški element tranzistor, ki je počel isto, a je bil bistveno manjši. Naslednji velik korak je bila iznajdba integriranega vezja leta 1958. Gre za vezje z množico pasivnih (upori, kondenzatorji) in aktivnih (diode, tranzistorji) elementov, ki jih natisnemo na skupni substrat iz polprevodniškega materiala. Glavna prednost elektronskih vezij je enostavnejša in cenejša izdelava, manjša velikost, nizka poraba energije in večja zanesljivost.

Vse od iznajdbe pa do modernih časov se je zmogljivost integriranih vezij povečevala eksponentno, kar je leta 1965 Intelov soustanovitelj Gordon Moore opisal z zakonom, da se število tranzistorjev na vezju (in s tem približno tudi računska moč) podvoji vsakih 18–24 mesecev.

Čeprav gre za povsem empirično opažanje, je doslej dobro držalo. Moorov zakon je nadvse pomemben pri načrtovanju in raziskavah, saj pri uporabi računalnikov implicitno privzamemo, da se bo zmogljivost v naslednjih dveh letih podvojila (ali pa cena razpolovila, odvisno od perspektive). Če je neki izračun prezahteven za trenutno dostopno računsko moč, bi pa šel s tisočkrat večjo – morate počakati le 20 let.

Tranzistor, čip, integrirano vezje, rezina, jedro

Tranzistor je torej osnovni elektronski element in v vsakem čipu ali vezju jih najdemo ogromno. V modernih procesorjih jih je več milijard. Precej večjo zmešnjavo pa povzročata termina integrirano vezje in čip, ki se uporabljata precej pomešano. Razlog za to je preprost.

Gre za isto stvar. Prvotno poimenovanje je bilo integrirano vezje, s čimer se označuje izdelek, ki nastane po obdelavi silicijeve rezine in nanosu vseh elektronskih komponent in povezav. A ker so običajno ta vezja zapakirana oziroma zalita s plastiko, se je uveljavil žargonski izraz chip, ki je potem našel pot tudi v slovenščino kot čip.

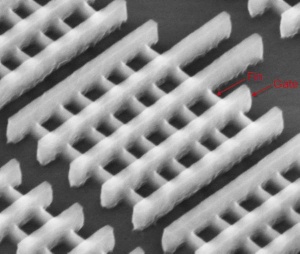

Mikroskopska slika klasičnega tranzistorja.

Silicijeva rezina (wafer) ali tudi substrat je tanek kos izjemno čistega silicijevega kristala, ki se uporablja pri izdelavi integriranih vezij. Rezine dobijo takšno ime, ker nastanejo iz dveh metrov visokega ingota monokristalnega silicija s premerom 30 cm, ki jih potem narežejo na tanke rezine.

Potem so tu še jedra (dice, v ednini die), ki se včasih prevajajo tudi v čipe. Gre za gole čipe, ki vsebujejo celotno funkcionalno integrirano vezjo in jih dobimo z rezanjem rezin na enake kose. Ko jedro oblečemo v plastiko, dobimo čip.

Manj je več

Poglavitni razlog za eksponentno večanje zmogljivosti je bila miniaturizacija vezij. Res smo bili v tem času priče številnim drugim izboljšavam, ki so današnje MOSFETe (kovinsko oksidni polprevodniški tranzistor na poljski efekt) na integriranih vezij izpopolnile do obisti, a ti so prinašali linearne pospeške. Glavni razlog za eksponentno pohitritev je zmanjševanje velikosti tranzistorjev, zaradi česar so jih na enako površino lahko stisnili več in ustrezno pohitrili čip.

V zadnjem času pa Moorovemu zakonu grozi upokojitev, ker se pri razvoju bližamo fizikalnim mejam. Tu ne gre za filozofsko vprašanje, ali je nadaljnji razvoj v trenutnem tempu še mogoč, temveč za preprosto fiziko. Današnji čipi so pretežno zgrajeni v 22 nm tehnologiji, na duri pa trka 14 nm. Če so bili pred tridesetimi leti elementi v čipih veliki en mikrometer (tisoč nanometrov), danes pa dobrih deset nanometrov, mar ne bodo čez desetletje manjši od nanometra? Žal ne.

Silicijev atom meri približno 0,2 nanometra. Tehnologija 22 nm izdelave pomeni, da je razdalja med različnimi komponentami v čipu okrog 22 nm. Razdalje znotraj tranzistorja so še bistveno manjše in obsegajo manj kot sto atomov. V modernih čipih je razdalja med vrati tranzistorja in substratom (iz materiala z visoko dielektričnostjo) okrog deset atomov! To pa je že problem iz dveh razlogov. Prvič, tehnologija izdelave ni stoodstotno zanesljiva. Vsak analizni kemik vam bo povedal, da je svet na atomski ravni skrajno umazan. Na površini, ki se zdi čista, boste vedno našli kak zablodel atom zlata, urana ali fosforja, prav tako boste tudi v vsakem monokristalu našli defekte, ki ne sodijo tja. Izdelati kristal silicija, ki nima defektov, je nemogoče. Kadar je posamezna aktivna plast debela nekaj atomov, pa se že vsak defekt lahko pozna kot nedelovanje.

Drugi razlog poznajo fiziki. Atomski svet je kvanten in tam vladajo drugačni zakoni kakor v makroskopskem svetu. Atomi so prav toliko delci kot valovi, še bolj pa to velja za elektrone, ker so lažji. Ena izmed najbolj zoprnih lastnosti je tuneliranje, ko lahko delec preide potencialno oviro, za katero klasično nima dovolj energije, a mu z neničelno verjetnostjo to v kvantnem svetu kljub vsemu uspe. Čim manj atomov opazujemo, tem izrazitejši so kvantni učinki, saj se ne izpovprečijo. Tuneliranje elektronov v tranzistorjih je nezaželeno, ker pomeni, da tranzistor ne prepušča toka, kakor zahtevamo od njega.

Primer 3D-dizajna zlaganja čipov v višino.

Prednosti 3D-čipov

• manjša poraba prostora

• krajše povezave, kar zmanjša zakasnitve

• premoščanje ozkega grla pri povezavi procesor-pomnilnik

• možnost horizontalnih in vertikalnih povezav

• višja prepustnost zaradi večjega števila možnih povezav

• nižja poraba energije

• heterogenost (možnost navpičnega nizanja različnih čipov)

Slabosti 3D-čipov

• težavnejše odvajanje toplote

• dražji dizajn zaradi kompleksnosti in pomanjkanja orodij

• težja izdelava in večji izmet

• pomanjkanje standardizacije

• večja možnost okvar (okvara enega dela povzroči nedelovanje celotnega vertikalnega sklopa)

• velike mrtve cone okoli TSV

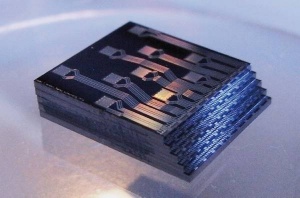

Tretja razsežnost

Ker pomanjševanje sestavnih delov čipa ni neomejeno možno, so inženirji staknili glave in našli staro rešitev – gradnjo v višino. Na enako površino lahko stisnemo več elementov, če jih postavimo v nadstropja. Pri tem je treba biti pazljiv, ker je oblikovanje takšnih čipov neprimerno bolj zapleteno, izdelava pa zaradi posebnih metod in večje natančnosti dražja. Posebno pozornost je treba nameniti tudi gretju, ki je pri kopičenju v treh dimenzijah bistveno večji problem. A načeloma so te težave rešljive.

V vezju dosežemo trirazsežnost na več načinov. Nekateri so sorazmerno preprosti in se uporabljajo že več let, drugi so tehnološko tako zahtevni, da jih še niso dovolj izpopolnili za komercialno rabo. Najprej si oglejmo razliko med 3D ohišji in 3D čipi.

3D ohišja

To je najnižja oblika tridimenzionalnosti, ki niti ni nova. Tej vrsti (3D packaging) se pravi tudi system-in-package (SIP) ali chip stack multi-chip module (MCM). Čipi so še vedno izdelani ločeno, potem pa jih postavijo drugega nad drugega. Povezave med njimi niso popolnoma nič drugačne kakor med čipi, ki so na vezju drug poleg drugega, le fizično so drug nad drugim. To precej omejuje število povezav med čipi in je primerno za čipe, ki potrebujejo le malo povezav. Tako lahko zlagamo pomnilniške čipe drugega nad drugega kot v pomnilniških karticah SD z visoko kapaciteto. Podobno je zgrajeno tudi tipalo CCD, ki ni nič drugega kakor do prosojnosti stanjšan čip, ki sedi na čipu za obdelavo slike. Podobno lahko pomnilniške čipe postavimo na logične oziroma procesorske čipe, kar je storil Apple v svojem A4.

3D integrirana vezja

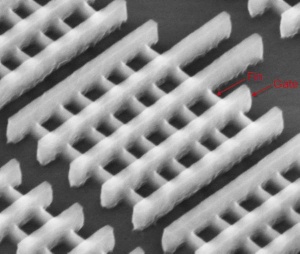

Bistveno zanimivejša je izdelava čipa, ki je tridimenzionalen že od začetka. Možnosti je spet več. Pogosto se uporabljajo tako imenovani TSV (through silicon via, kjer je via kratica v kratici in pomeni vertical interconnect access). Gre za navpične prevodne povezave, ki jih napravijo skozi silicij in povezujejo več plasti.

Pri izdelavi čipov začnejo s silicijevimi rezinami, ki jih dobijo z rezanjem ingota silicijevega monokristala na tanke kose (glejte tudi članek »Prihajajo superčipi!« v Monitorju 03/13). Če skozi rezino izvrtate luknjice in jih naprej obdate z izolatorjem, potem pa zalijete s prevodnim materialom, na primer bakrom ali volframom, ste dobili TSV. Ti so navadno široki od 1 do 10 mikrometrov, globoki pa desetkrat toliko. Celotno rezino je potem treba še stanjšati, da postanejo TSVji izpostavljeni. Ti potem rabijo za povezave med plastmi, a ima postopek precej slabosti.

Prvič, precej območja okrog TSV (mrtva cona) je neuporabnega zaradi načina izdelave. Izdelava lukenj v krhek monokristalni silicij lahko povzroča defekte v okolici, ti pa lahko uničijo rezino. Problem je tudi segrevanje v nadaljnjem postopku, saj ima baker petkrat večji razteznostni koeficient od silicija. To ustvarja napetosti, ki lahko povzročijo spremembo lokalne zgradbe in nezanesljivo delovanje čipa. Kljub temu je postopek precej napredoval in je komercialno že uporaben. Poznamo tri podrazličice: rezina-rezina (wafer-wafer), jedro-rezina, jedro-jedro (die-die), odvisno od tega, kaj se spaja. Združujemo lahko celotne rezine ali pa zgolj izrezane dele rezin, tako imenovana jedra (glej okvir za terminologijo).

Zanimiv način rabe TSV je tehnologija 2,5D. Tako se imenuje, ker je križanec med dvo- in pravo tridimenzionalno. Glavni čipi so še vedno razporejeni v ravnini osnovne rezine in nimajo nobenih tridimenzionalnih značilnosti. Nad njimi pa je položena povezovalna plast (interposer), ki ne vsebuje ničesar drugega kakor bakrene povezave in morda kak kondenzator. Ta je tridimenzionalna, prepredena s TSVji. Prednost tega postopka je to, da pri trenutnem stanju tehnologije prinaša najboljše iz obeh svetov. Čipi so zgrajeni po klasični metodi, ki je preverjena in izpopolnjena, obenem pa jih lahko posejemo zelo na gosto, ker ni treba skrbeti za povezave med njimi. Te so v drugi ravnini, kjer je prostora več kot dovolj. Če je polni 3D revolucija, je 2,5D evolucija trenutne planarne tehnologije in kot tak bistveno enostavnejši za izvedbo, hkrati pa predstavlja prvi korak na poti v 3D.

Glavni cilj pa je seveda monolitni, sekvenčni ali zaporedni 3D, kakor imenujemo način proizvodnje čipov, ki bodo tridimenzionalni že od same izdelave. Pri preostalih načinih namreč rezine obdelavo ločeno do konca in jih potem povezujemo. V tem primeru pa bi že na eno rezino vgradili več slojev povezav in elektronskih elementov, ki bi jim potem sproti dodajali rezine. V tem primeru odpade izdelava velikih in okornih TSVjev in natančno spajanje rezin ali jeder, ker so vsi elementi in povezave že proizvedeni skupaj. Povezav med elementi pa je lahko vsaj toliko kot v klasičnih čipih. Teoretična vertikalna povezljivost v monolitnem 3D čipu je lahko do 10.000-krat boljša od čipov s TSVji. Le izdelati jih je treba nekako.

Na tem področju je med vodilnimi inštitut Cea-Leti iz Grenobla v Franciji. Glavni problem take izdelave, ki se sliši precej enostavno – na obdelano rezino nanesemo dodatno plast silicija in ponovimo postopek – je temperaturna obstojnost. Priprava silicijeve plasti (dopiranje) poteka pri visokih temperaturah, ki bi uničile spodnje elemente. Cea-Leti je pripravil postopek, kjer to počno z nekoliko nižjimi temperaturami, a rezultati so še precej oddaljeni od komercialne rabe.

Kako deluje tranzistor

Tranzistor je osnovni elektronski element, ki je omogočil razvoj elektronike. Njegovo delovanje si najlaže predstavljamo tako, da najprej pogledamo diodo, ki je elektronski element z dvema priključkoma. Silicij v eni plasti diode je dopiran tako, da ima presežek pozitivnih nabojev (p-plast), druga plast pa negativnih nabojev (n-nabojev). Na stiku se vrzeli iz prve plasti in presežek elektronov iz druge plasti nevtralizirata, zato nastane zaporna plast, v kateri je električno polje, ki preprečuje nadaljnji električni tok. Če diodo na enosmerno napetost priključimo tako, da električno polje v zaporni plasti še povečamo, tok skoznjo ne bo tekel. Dioda zato prepušča električni tok samo v eni smeri (anoda na pozitivni pol in katoda na negativni pol), v drugi smeri pa ne, razen če je pritisnjena napetost tako visoka, da pride do preboja in diodo uničimo.

Tranzistorjev je več vrst, najpomembnejša pa sta bipolarni (BJT) in kovinsko oksidni polprevodniški na poljski efekt (MOSFET). Bipolarne tranzistorje si lahko predstavljamo kot dve diodi. Glede na orientacijo so sestavljeni iz plasti pnp ali npn, ki jih imenujemo emitor, baza in kolektor. Poenostavljeno povedano tranzistor deluje kot stikalo oziroma ojačevalnik. Če je na npn tranzistorju med bazo in emitorju dovolj visoka napetost, tako da je baza bolj pozitivna, bo tranzistor prevajal tok. Večina elektronov bo tekla iz emitorja v kolektor, le manjši del pa v bazo.

Druga pogosta vrsta tranzistorjev, ki jih danes praktično edine najdemo v integriranih vezjih, so MOSFET-i. Ti spadajo v skupino unipolarnih tranzistorjev ali tranzistorjev na poljski efekt (FET) in delujejo drugače kakor bipolarni tranzistorji. Krmilimo jih napetostno z električnim poljem in ne z baznim tokom. Sestavljajo jih trije priključki: izvor, vrata in ponor. Poenostavljeno povedano je prevodnost med izvorom in ponorom odvisna od napetosti (električnega polja) med vrati in izvorom, skoznju pa tok ne teče.

3D NAND

Pomnilnik NAND, ki ga uporabljamo v pogonih SSD, je bil eno prvih področij, kjer je 3D postal nuja. To je posledica njegovega proizvodnega postopka, ki praktično ne dovoljuje zmanjšanja pod 16 nm tehnologijo izdelave. Za nadaljnje povečevanje zmogljivosti je bil zato prehod v tri dimenzije nujen.

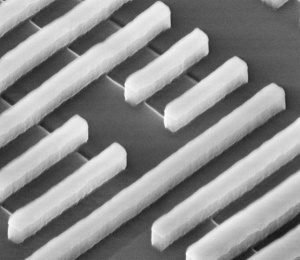

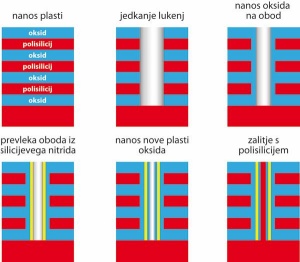

Postopek izdelave 3D NAND-a, ki ga uporablja Samsung.

Samsung je bil lani prvi, ki je pokazal delujoče 3D čipe NAND, letos pa jih že pridno vgrajujejo v svoje SSDje zmogljivosti 1 TB. Tehnologija, ki sploh ni nova, saj jo je Toshiba predlagala že leta 2007, je do danes tako napredovala, da lahko sestavijo 32 plasti NANDa. Kot pravijo v Samsungu, novi pogoni zaradi te novosti porabijo 20 odstotkov manj energije in so dvakrat vzdržljivejši od pogonov s planarnim NANDom.

Zvijača pri izdelavi 3D NANDa je, da planarne celice prepognemo in zasučemo za 90 stopinj, da stojijo navpično, tako da porabijo manj prostora. Proizvodnja poteka v več stopnjah. Najprej na silicijevo rezino nanesejo plast CMOSa (komplementarni kovinsko oksidni polprevodnik) z ustreznimi čipi za logiko in povezavami med njimi. Čezenj položijo plast neprevodnega silicijevega dioksida, plast prevodnega polisilicija in tako izmenjaje naprej. Ko je število plasti zadostno, skoznje navpično izjedkajo luknje do dna. Te potem po celotnem obodu obdajo s silicijevim dioksidom. Na to plast na obodu potem nanesejo silicijev nitrid, pa še eno plast silicijevega dioksida. Na koncu preostalo luknjo zamašijo s prevodnim polisilicijem. To je zelo natančna in občutljiva metoda, a na koncu dobijo vertikalni NAND, katerega zmogljivost je odvisna od števila plasti. Doslej so pri številki 32.

Intelov 3D-tranzistor

Mikroskopska slika Intelovega 3D tranzistorja.

Intel je leta 2012 predstavil 3D-tranzistorje, ki so vgrajeni v procesorje družine Ivy Bridge in novejše. Poimenovali so ga Tri-Gate, kar najlepše opisuje njegove lastnosti. Od običajnih MOSFET-ov se razlikuje po vratih, ki sedaj niso ena na vrhu tranzistorja, ampak imajo tri priključke: dva na straneh in enega na vrhu, kar omogoča bolj razgibano vezavo tranzistorja v vezje. Vseeno pa so čipi, v katerih najdemo te tranzistorje, še vedno 2D.

Kje smo

Kot vidimo, oznaka 3D pri izdelavi integriranih vezij oziroma čipov označuje zelo različne tehnologije. Vsem pa je skupen cilj na isto površino spraviti čim več elementov, da bi lahko še naprej povečevali hitrosti in zmogljivosti elektronskih naprav. Pomnilniški čipi so že precej dobro zakorakali v 3D svet, logični čipi pa so še nekoliko oddaljeni od pravega 3D. So pa vmesne tehnologije (2,5D, TSV) prav tako vzpodbudne. Za zdaj kaže, da je Moorov zakon dobil še nekaj let odloga pred upokojitvijo.